新闻网讯 近日,集成电路学院刘冬生教授团队在CMOS振荡器领域取得新进展,相关成果以“A Low-Phase-Noise Wide-Tuning-Range Mode-Switching Oscillator Using Multi-Magnetic-Coupling and Active-Source-Degenerating Techniques”为题,被集成电路设计领域顶级期刊IEEE Journal of Solid-State Circuits(JSSC)接收。刘冬生为论文通讯作者,集成电路学院博士生单晓煜为论文第一作者,集成电路学院为论文第一完成单位。

随着无线通信技术的发展,兼容多通信协议标准的低噪声超宽频射频收发机对于进一步提升通信速率,减小无线终端尺寸具有重要的意义。锁相环作为射频收发机中的关键模块,产生用于调制解调的高频信号,其噪声性能和频带覆盖,是决定射频收发机性能的关键因素。CMOS数控振荡器是锁相环中的核心模块,其输出信号的相位噪声性能及可调频率范围在很大程度上决定了锁相环输出信号抖动及频段覆盖。当前的CMOS低噪声超宽频振荡器主要基于模式切换技术,通过多核心耦合,以提升功耗为代价,提高频率调谐范围和相位噪声性能。

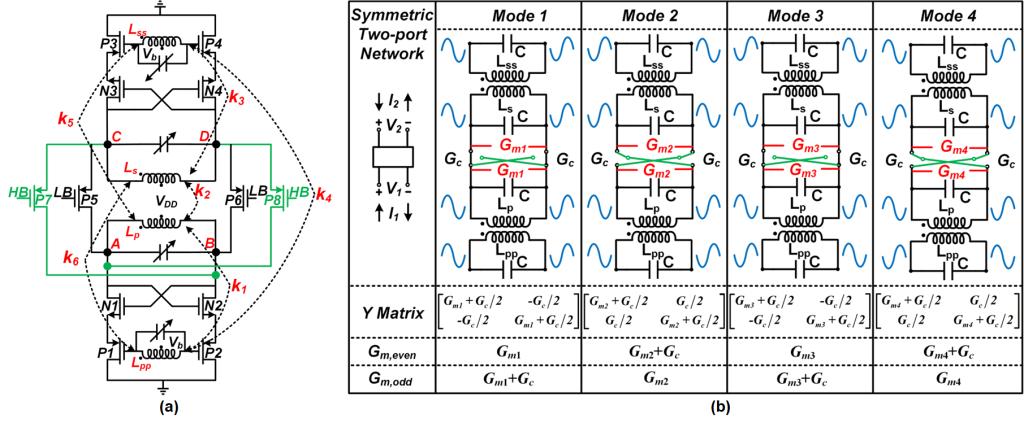

图为振荡器架构和振荡模式设置

团队在传统模式切换技术的基础上,提出多线圈耦合技术,解决奇模下等效品质因数退化的问题。同时,采用有源源极退化架构,在不增加功耗的基础上,进一步提升振荡器相位噪声性能。在理论贡献方面,建立非对称多线圈耦合理论模型,澄清传统噪声循环架构中存在的理解偏差,提出有源源极退化的概念,给出对应的相位噪声数学表达。

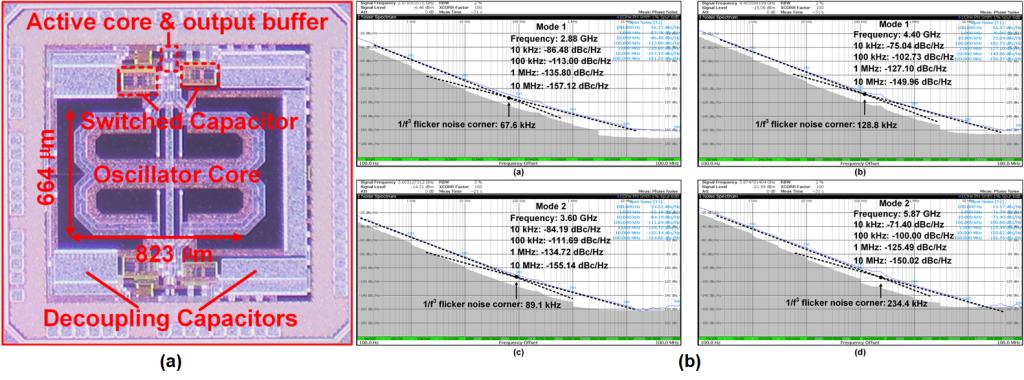

图为芯片显微照片和振荡器相位噪声测试结果

如上图所示,团队设计的振荡器最优FoMT为209.5 dBc/Hz @ 10 MHz, 在68.3 %的频率调节范围内的1/f3 corner为68 ~ 234 kHz。振荡器优值达到了该领域同类研究中的顶尖水平。

集成电路学院刘冬生教授主要从事后量子密码芯片、高速互连集成电路和射频收发器芯片关键技术(如时钟恢复、频率综合器、振荡器、射频前端)等方面的研究,近5年成功投片20余次,近5年主持国基金重点项目、国家重点研发课题、华为合作等千万级项目2项,百万级项目11项;出版专著1本,在IEEE TII、IEEE IoT、IEEE TIE、TCAS I、JSSC、CICC、ASSCC、ISCAS 等期刊及高级别会议上发表论文60余篇;授权专利63项,国际PCT专利2项,美国专利1项,专利转让6项。研究成果在海康等13家企业进行了应用和推广,累计应用价值35.4亿元,2023年获湖北省科技进步二等奖(第一完成人)。刘冬生还担任IEEE Senior Member,国家集成电路丛书编委,国际期刊“Microelectronics Journal” Editor、“微电子学”期刊编委,IEEE APCCAS、IEEE ASICON、IEEE ICSICT、AsianHOST2023 等国际会议技术委员会委员;2023年获得华为火花奖。